3.4.Building a Datapath

\(3.4.\)Building a Datapath

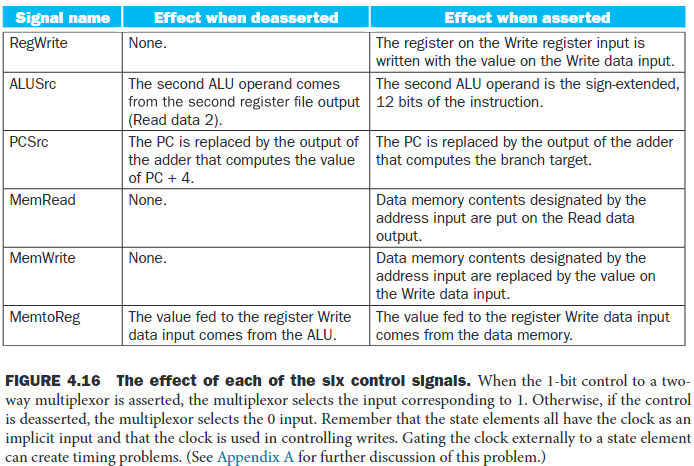

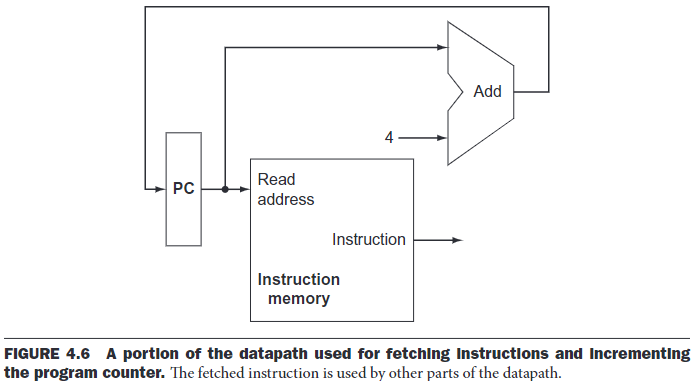

1.Basic devices

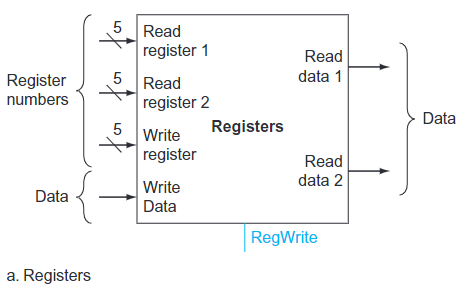

Registers: It contains:

Two data words from the register file, and write one data word into the register file for each instruction.

An input. It specifies the register number to be read.

An output. It carries the value that has been read from the register.

To write a data word, we need two more inputs: one to specify the register number to be written and one to supply the data to be written into the register.

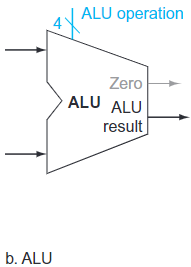

- ALU

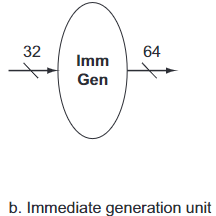

- Immediate generation unit: In operations like

addi x1 x2 10, the immediate number10is written in 12-bit offset in the instruction. So we need to sign-extend the number to a 64-bit signed value. The Imm-Gen does the job:

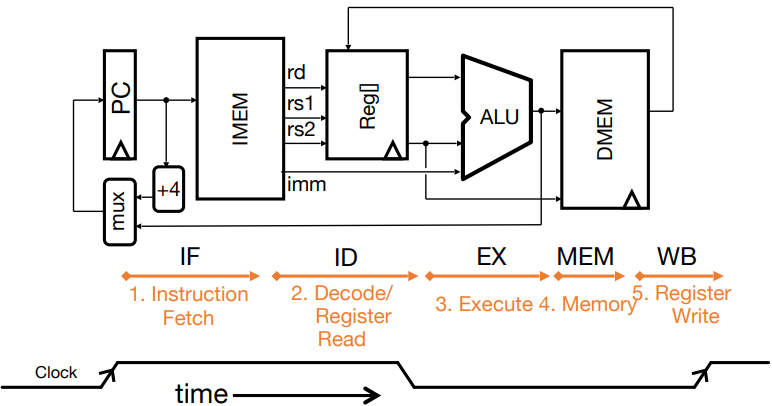

2.Basic phases of instruction execution

The phases of instruction execution can be divided into 5 parts:

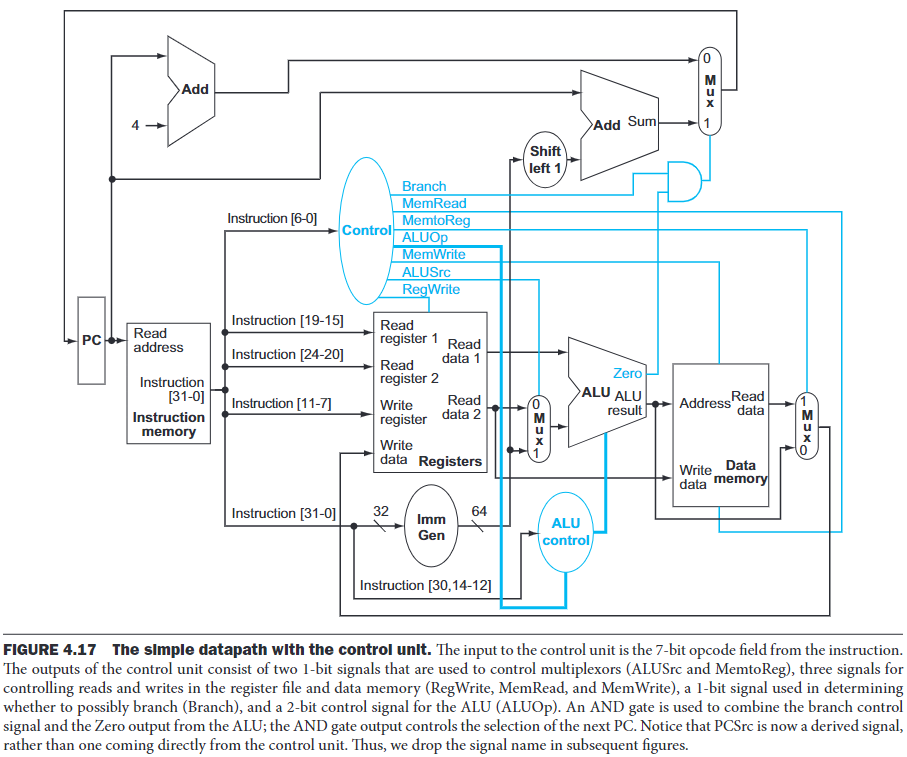

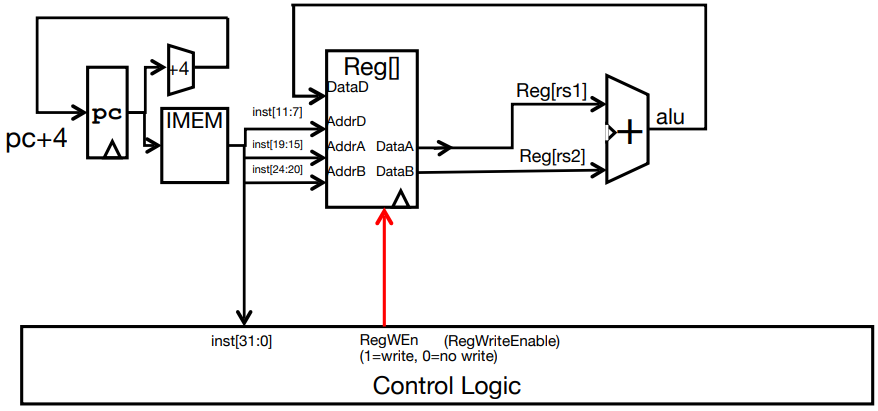

3.Implementation of different statement

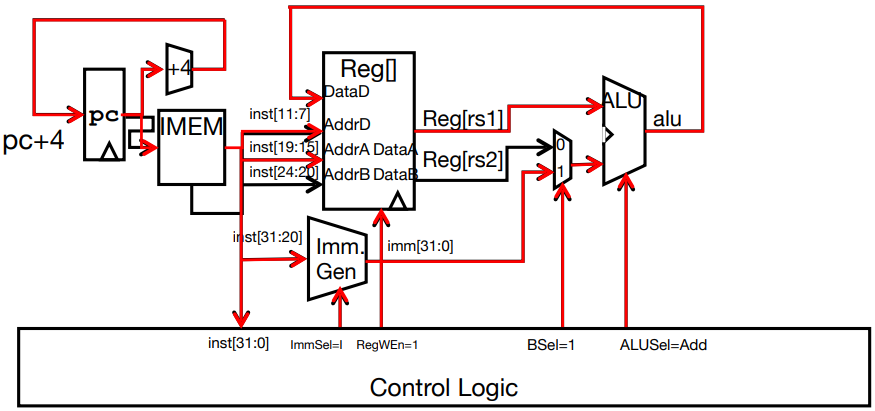

\(a.\)Add instruction

The add is simple, we just get value from

DataA and DataB, and calculate the result by

ALU.

To perform addi, we get one of out input from Imm-Gen

rather than DataB. The source of Imm-Gen is from

IMEM, from which we can get the instruction, and

inst[31:20] is the immediate we want:

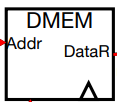

\(b.\)load &

save instruction

To implement the instructions, we can add a DMEM to

read or write data.

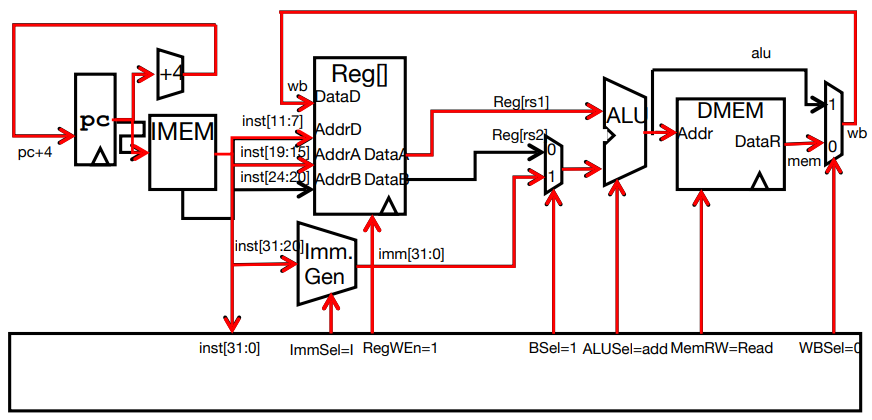

DMEM: It's input isAddrand outputsDataR. When in "read" mode, it gets information from the address. Else, it writes the information into the address:

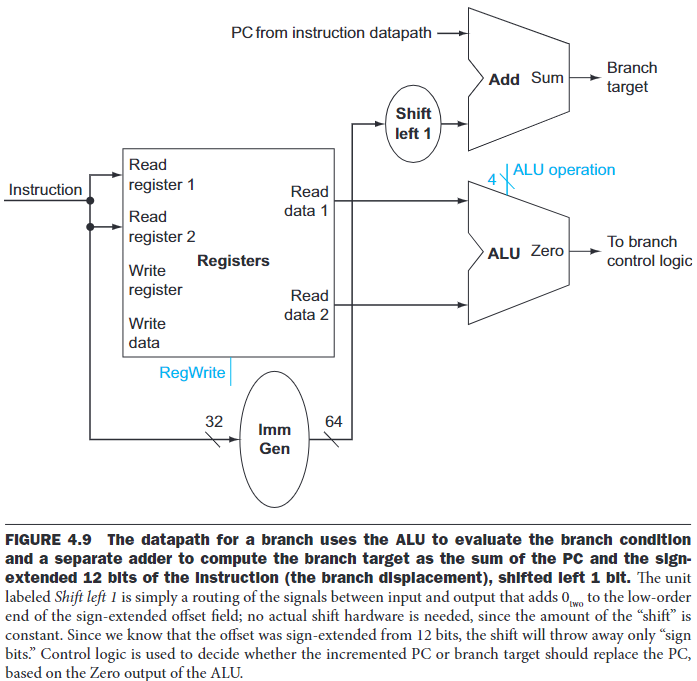

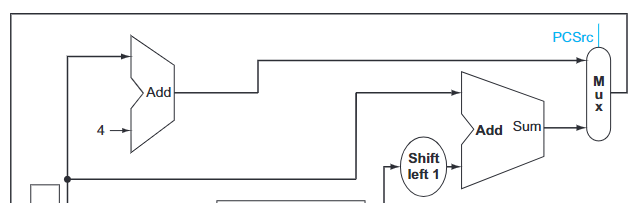

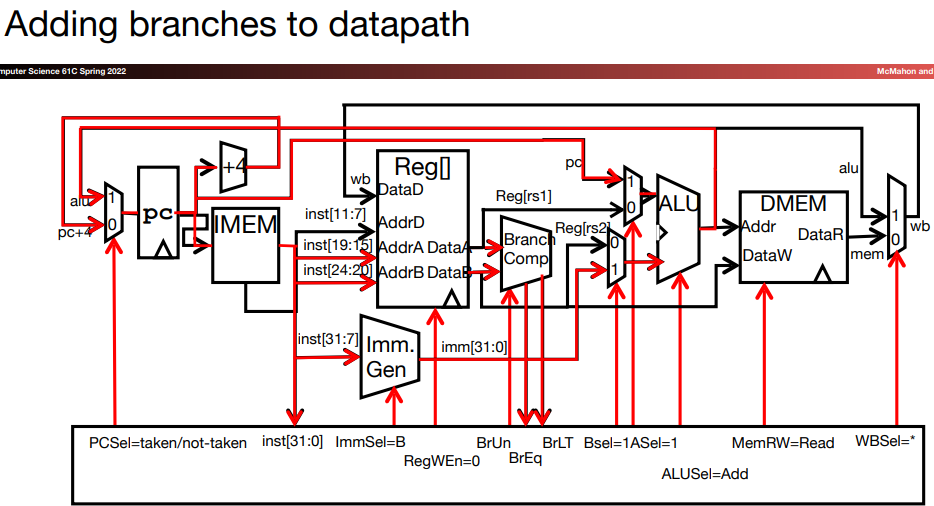

\(c.\)Branch instruction

The basic form of branch instruction is

beq x1 x2 offset. To implement this instruction, we must

compute the branch target address by adding the sign- extended

offset field of the instruction to the PC. There are two

details in the definition of branch instructions to which we must pay

attention:

The instruction set architecture specifies that the base for the branch address calculation is the address of the branch instruction.

The architecture also states that the offset field is shifted left 1 bit so that it is a half word offset; this shift increases the effective range of the offset field by a factor of 2.

If the branch condtion is true, the branch target address becomes the new PC, and we say the branch is taken. Else, we say the branch is not taken.

We first get the address of PC+4 and branch through

this struction:

To select from multiple address, we use a multiplexor and control signal

Combined with the previous struction, we get this design:

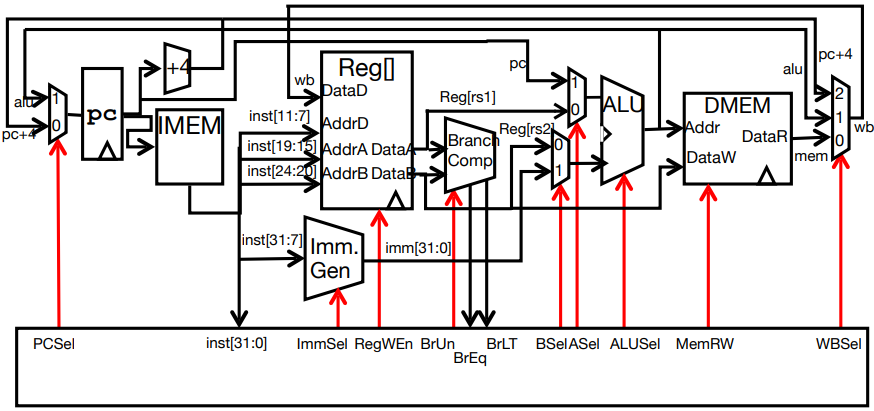

\(d.\)jal &

jalr instructions

jalr does the following things:

Set

PC=Reg[rs1]+immediate- Uses same immediate as arithmetic and loads. No multiple by 2 bytes!

Set

PC=PC+offset- Since the offset is calculated by ALU, we connect the output of ALU with input of PC.

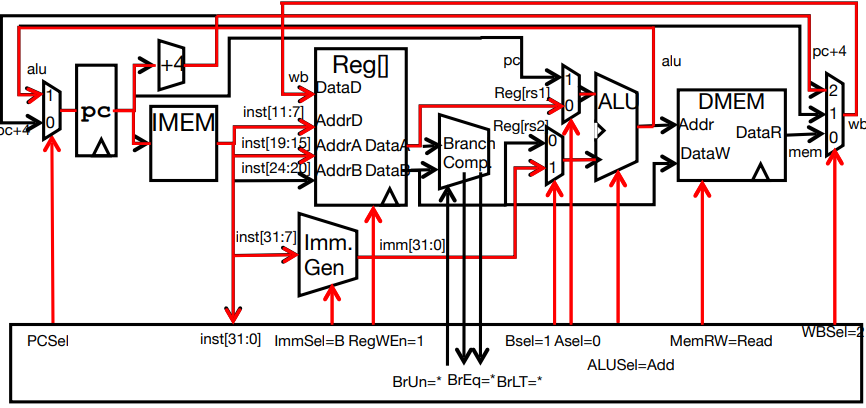

jal does the following things:

- Save

PC+4inReg[rd](namelyDataD) - Set

PC=PC+offset

4.Datapath control