5.6.Cache Coherence

5.6.Cache Coherence

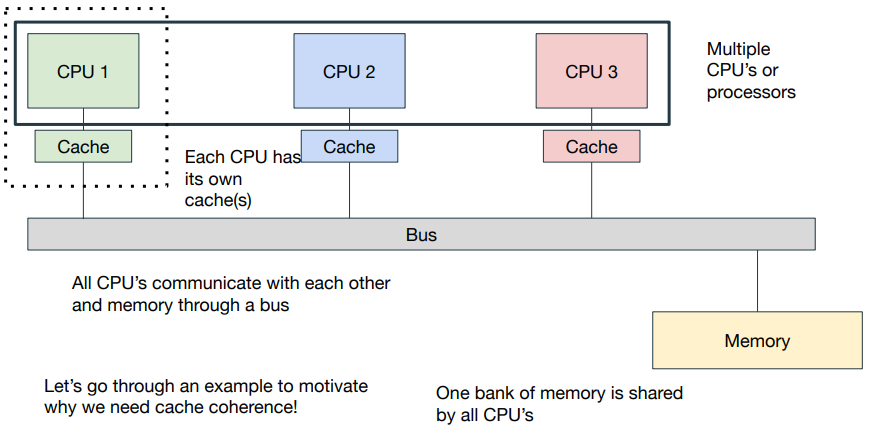

1.Cache model

2.Coherence concept

\(a.\)Coherence in detail

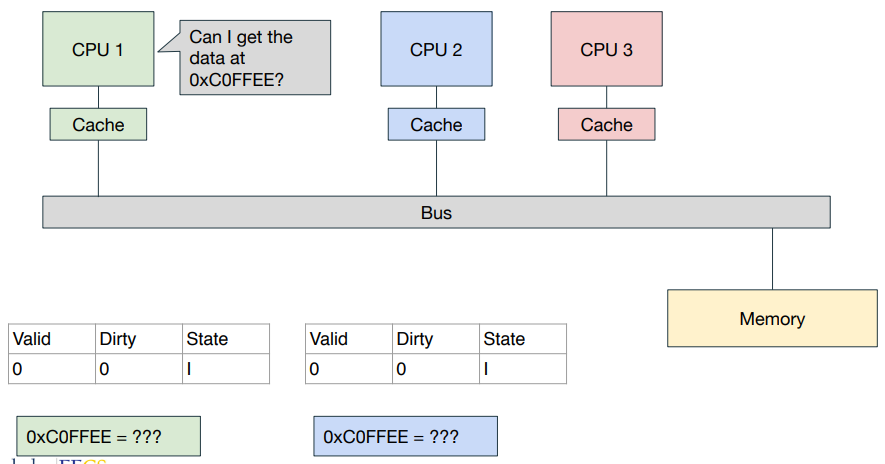

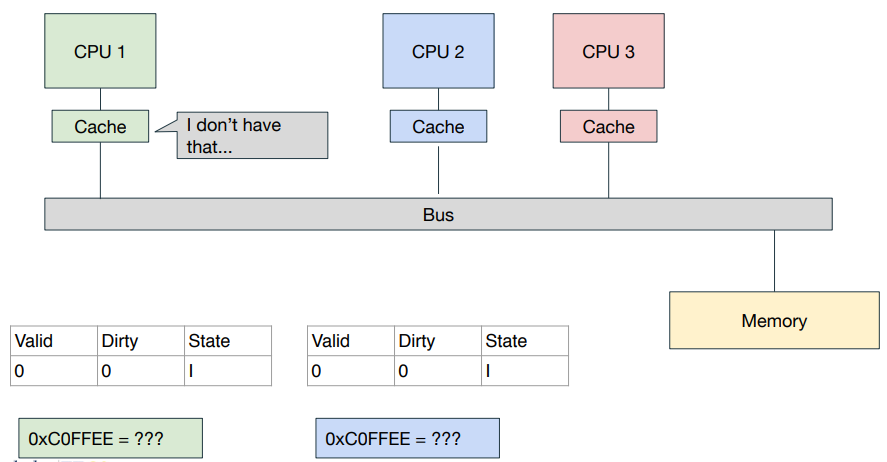

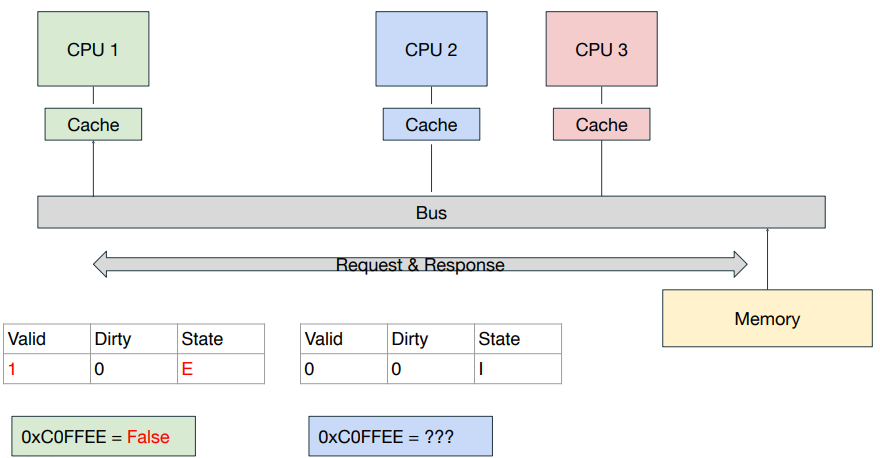

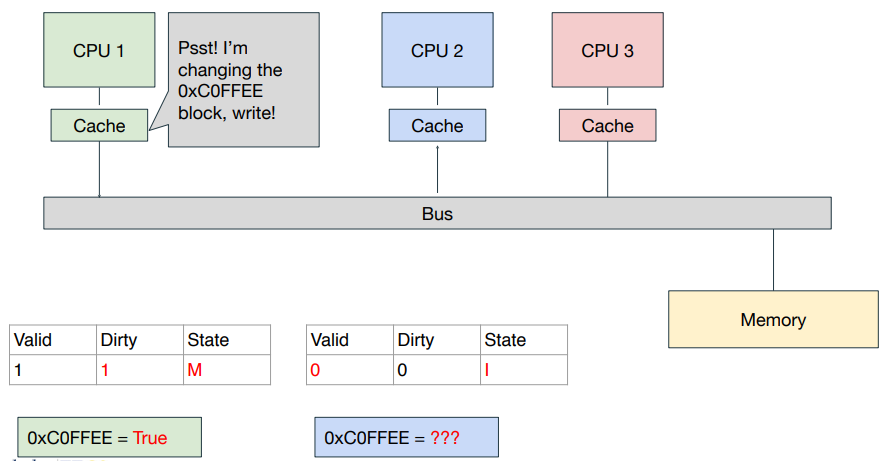

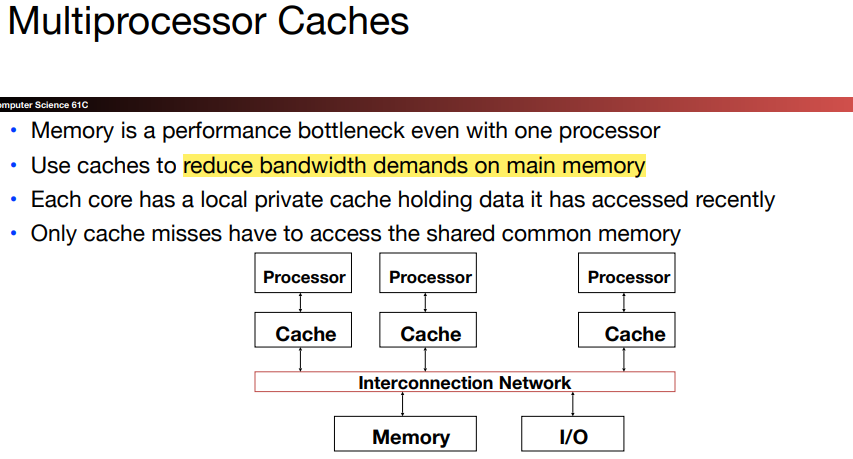

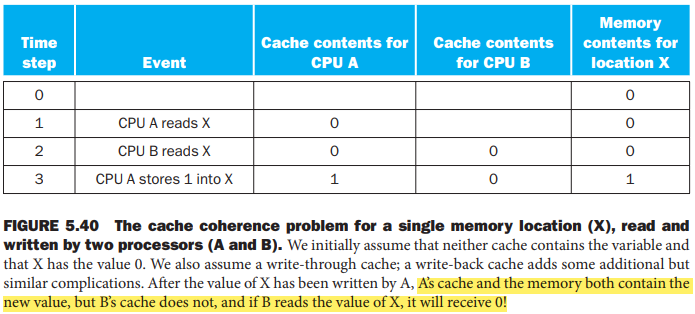

Caching shared data introduces a new problem. The following is an example:

The two different processors have two different values for the same location, this is referred to as cache coherence problem.

Informally, we could say that a memory system is coherent if any read of a data item returns the most recently written value of that data item. This simple concept contains two different aspects of memory system behaviour:

- coherence: defines what values can be returned by a read.

- consistency: determines when a written value will be returned by a read.

A memory system is coherent if:

- A read by a processor P to location X that follows only one write by P to X always returns the value written by P.

This preserves program order.

- A read by a processor to location X that follows only one write by another processor to X returns the written value if the read and write are sufficiently separated in time.

This defines memory coherence.

- Writes to the same location are serialized; that is, two writes to the same location by any two processors are seen in the same order by all processors. For example, if CPU B stores 2 into memory at address X after time step 3, processors can never read the value at location X as 2 and then later read it as 1.

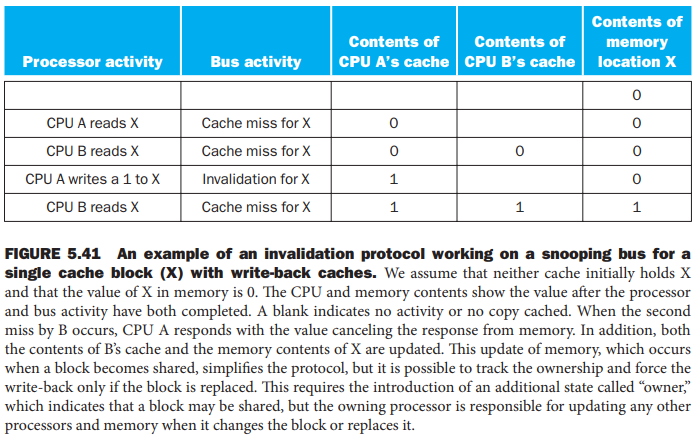

\(b.\)Snooping-based cache coherence

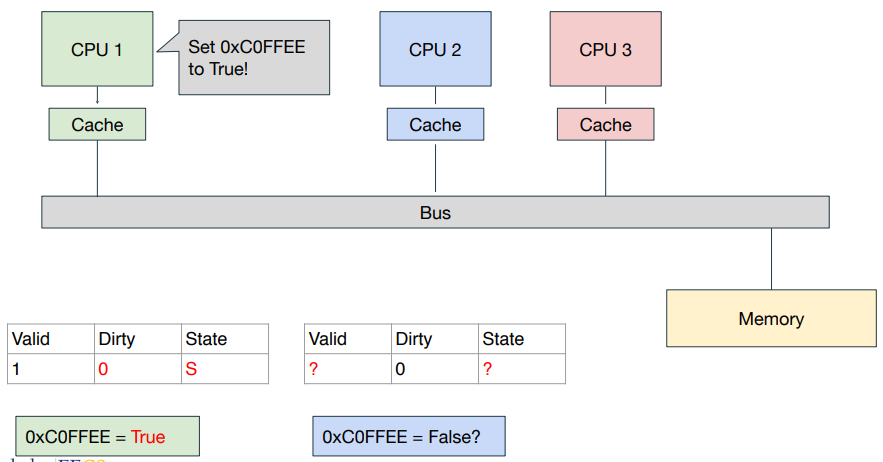

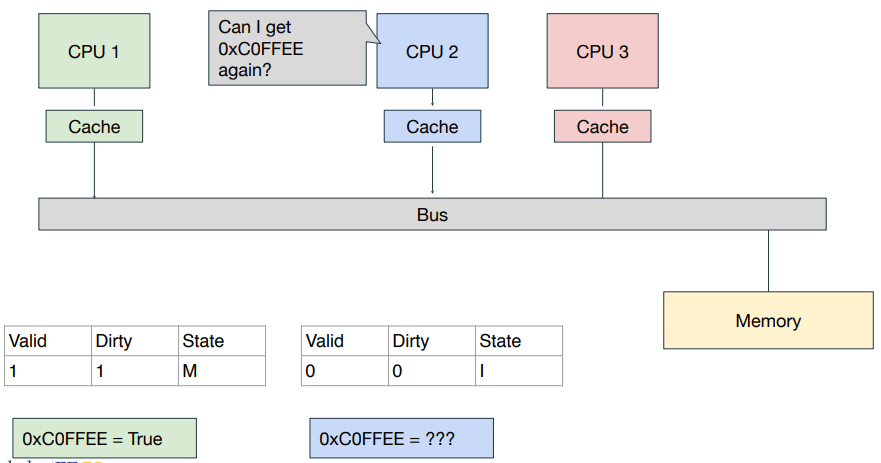

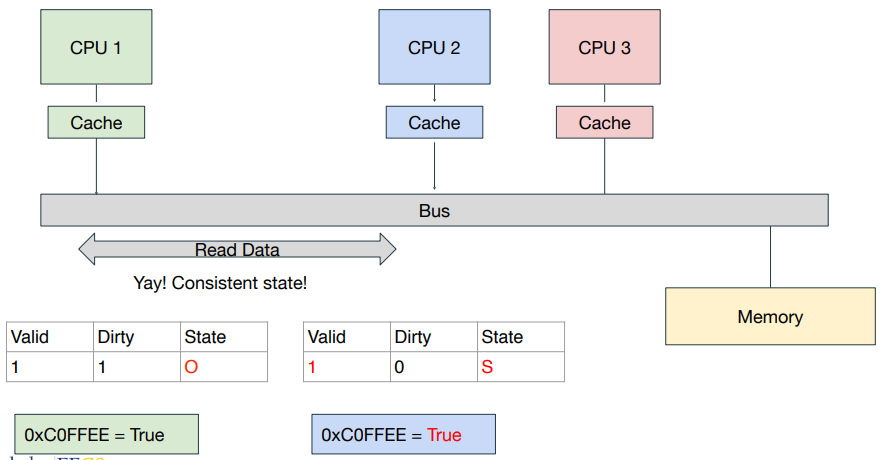

One method of enforcing coherence is to ensure that a processor has exclusive access to a data item before it writes that item. This style of protocol is called a write invalidate protocol because it invalidates copies in other caches on a write.

Take the same example before, when we write 1 into location X by CPU A, the CPU B will get a cache miss, and is forced to fetch a new copy of data:

Block size plays an important role in cache coherency. Large blocks can cause what's called false sharing, when two unrelated shared variables are located in the same cache block, the whole block is exchanged between processors even though the processors are accessing different variables.

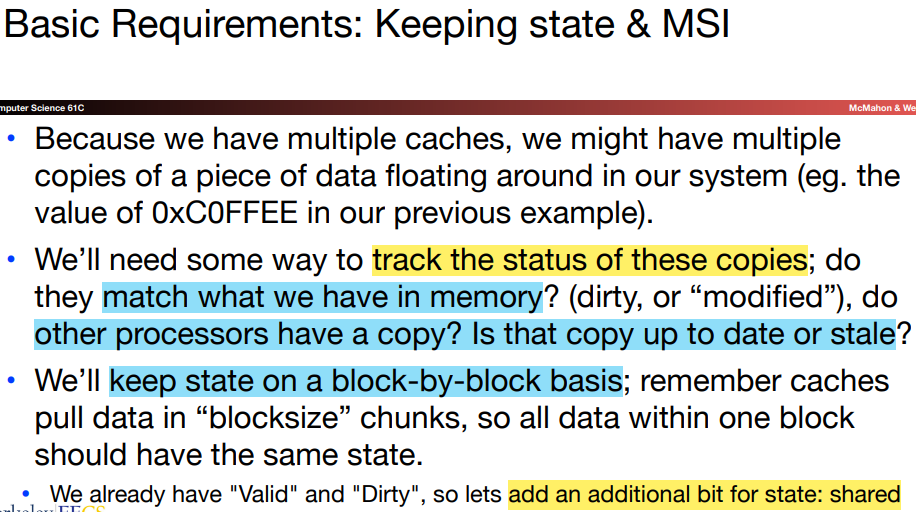

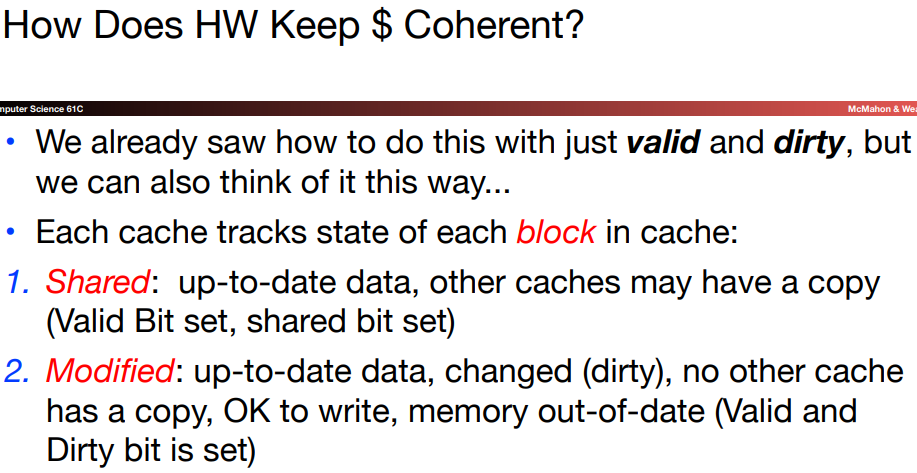

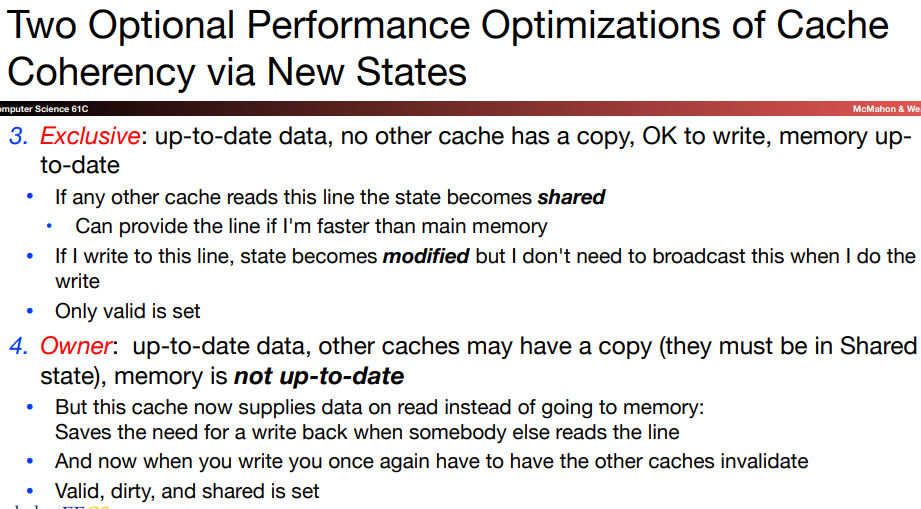

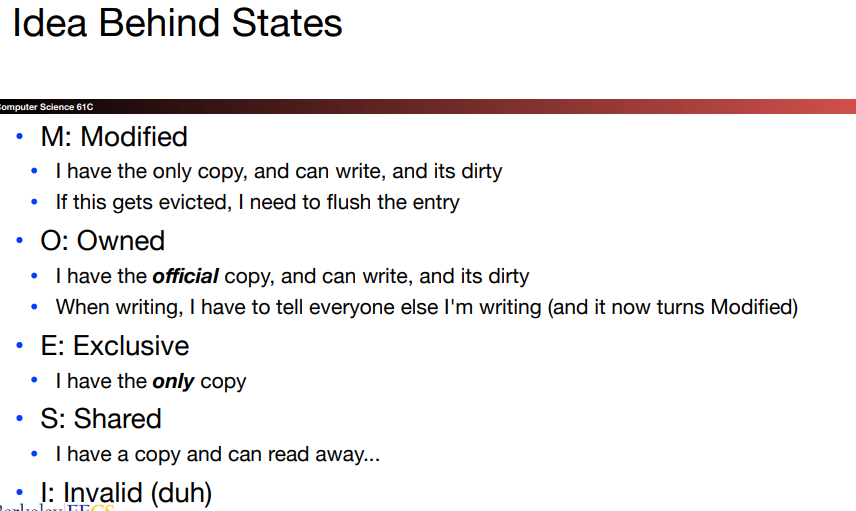

3.MOSEL cache coherency protocol:

\(a.\)Protocol design

\(b.\)Basic concepts

\(c.\)Example