9.1~9.3.VM Address Space

\(9.1 \sim 9.3\)VM Address Spaces

1.Terminologies

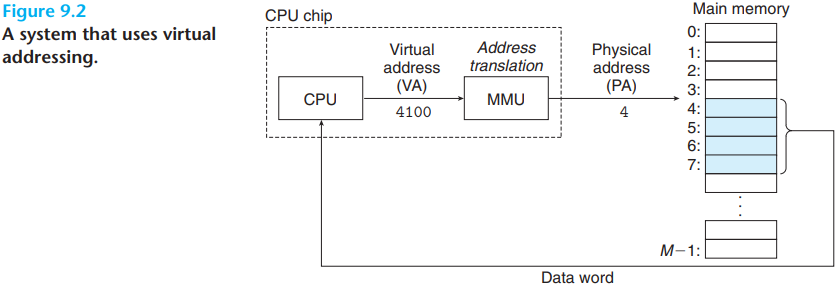

Each byte has a unique physical address(PA).

VA: Virtual Address.

The activity of transferring a page between disk and memory is known as swapping or paging.

Pages are swapped in(paged in) from disk to DRAM, and swapped out(paged out) from DRAM to disk.

The strategy of waiting until the last moment to swap in a page, when a miss occurs, is known as demand paging.

An address space is an ordered set of nonnegative integer addresses:

- If the integers in the address space are consecutive, then we say that it is a linear address space.

\[ \lbrace 0,1,2, \cdots \rbrace \]

A virtual address space with \(N = 2^n\) addresses is called an n-bit address space.

At any point in time, the set of virtual pages is partitioned into three disjoint subsets:

Unallocated

Cached

Uncached

2.DRAM Cache Organization

\(a.\)Page tables

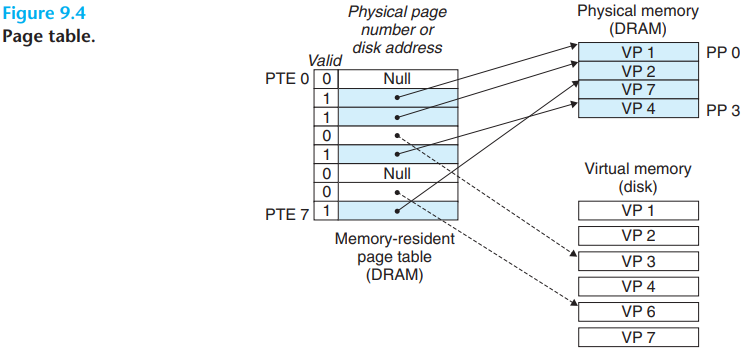

A page table is an array of page table entries(PTEs). Each page in the virtual address space has a PTE at a fixed offset in the page table.

The valid bit indicates whether the virtual page is currently cached in DRAM.

- If the valid bit is set, the address field indicates the start of the corresponding physical page in DRAM where the virtual page is cached.

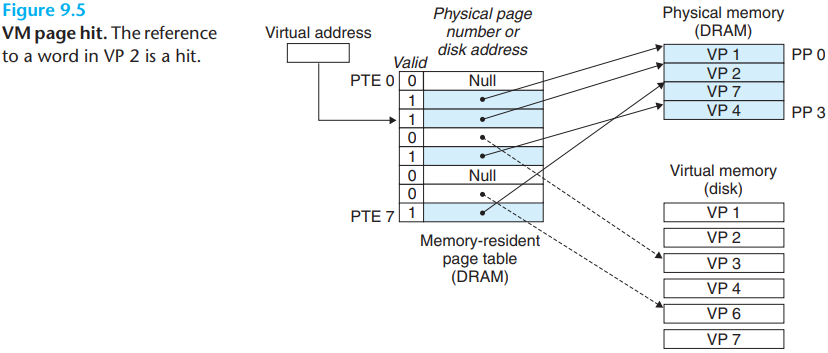

\(b.\)Page hits

- The address translation hardware uses the virtual address as an index to locate PTE 2.

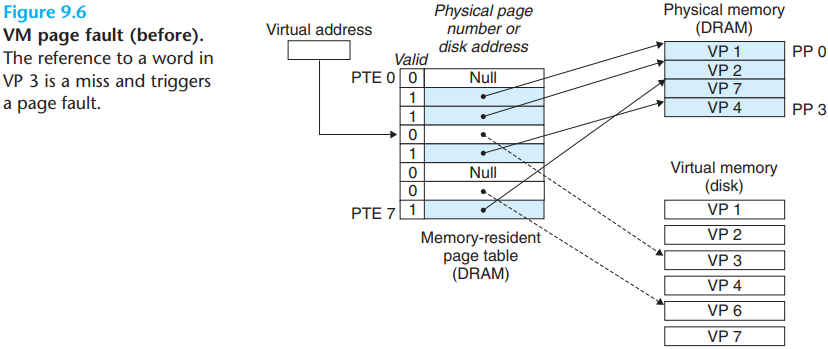

\(c.\)Page faults

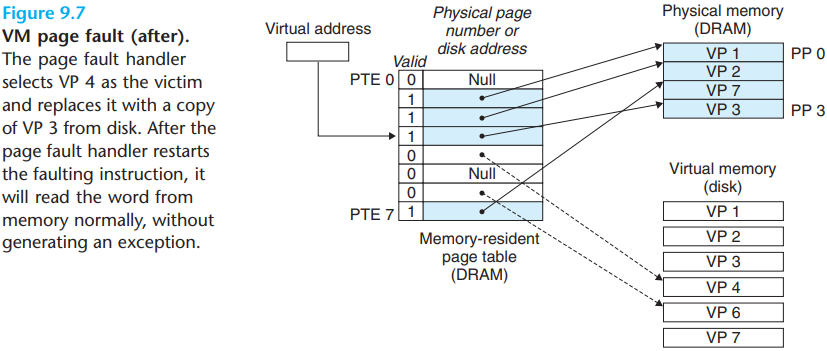

The page fault exception invokes a page fault exception handler in the kernel, and it selects a victim page. In this case, it's VP4 in PP3.

If VP 4 has been modified, then the kernel copies it back to disk.

The kernel modifies the page table entry for VP 4 to reflect the fact that VP 4 is no longer cached in main memory.

Next, the kernel copies VP 3 from disk to PP 3 in memory, updates PTE 3, and then returns.

- When the handler returns, it restarts the faulting instruction, which resends the faulting virtual address to the address translation hardware. But now, VP 3 is cached in main memory, and the page hit is handled normally by the address translation hardware.