1.4.硬件描述语言

\(1.4.\)Hardware description language

1.Logic gate

- An elementary logic gate is an elementary chip which is designed to deliver a well-defined functionality.

- A composite logic gate is one which is made up from elementary logic gate and other composite logic gates.

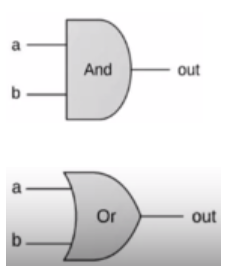

The AND gate, OR gate and

NOT gate can be represented by these diagrams:

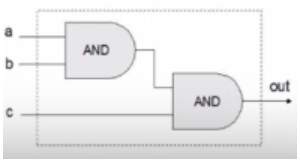

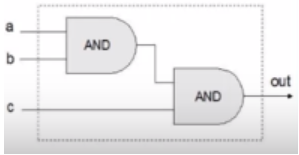

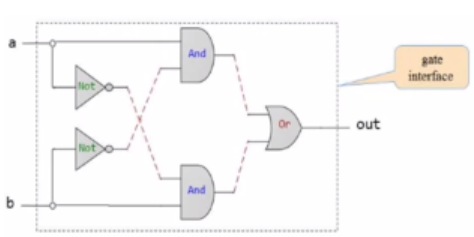

By connecting the elementary gate together, we can get composite gates that have more complicated funtionality. For example:

2.HDL

\(a.\)Intro

We can actually build and implement the logic gates using a formalism called Hardware Description Language or HDL. Once you build a logic gate in HDL,you can actually simulate it, test it.And finally,build it in hardware.

The hardware description of a logic gate contains these structure:

- Interface: It describe what the chip takes in as input and the output.

- Implementation: It describe how the chip achieves its functionality.

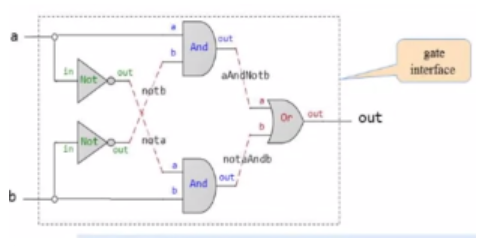

For example the gate below can be describe as :

1 | CHIP Xor { |

\(b.\)Diagram development

Then how can we develop a diagram through its functionality description? The following steps might help:

draw the boundary of the chip diagram.

- we use this dash to outline for this purpose and what remains outside the boundary is the user's view of this gate. In other word,the,the gate interface.All the users knows is that he or she has a gate that has two inputs,a and b,an output called out and altogether.They somehow, this chip as if by magic,delivers Xor functionality

Notice how the a signal is being copied and sent simultaneously into two different destinations.Take a as an example, one of them is sent to

Andgate and the otherNotgate.Whenever you use an off-the-shelf gate,you are bound to use the names of the gate's input and output as advertised.

- In other words, the gate comes along with what can be called the gate's signature or the gate's APl. So we have no degrees of freedom here.

The red connections are use to connect the different chip parts together. The rule is that every one of these connections has to be named and it's our responsibility to come up with self-descriptive names.

\(c.\)Some features

The interface of one chip is unique. That's because there's only one way to describe the chip.

The implementation of one chip is not unique, however.

HDL is a functional or declarative language. There is no procedure going on.There's no program execution going on. It is nothing more than a static description of the gate diagram.

- So because HDL is a functional language,we can actually write those HDL statements in any order that we wish.